用一篇3线~8先译码器74LS138和基本逻辑电路构成一位全加器电路,画出电路连线图

来源:学生作业帮 编辑:拍题作业网作业帮 分类:物理作业 时间:2024/04/30 16:50:57

用一篇3线~8先译码器74LS138和基本逻辑电路构成一位全加器电路,画出电路连线图

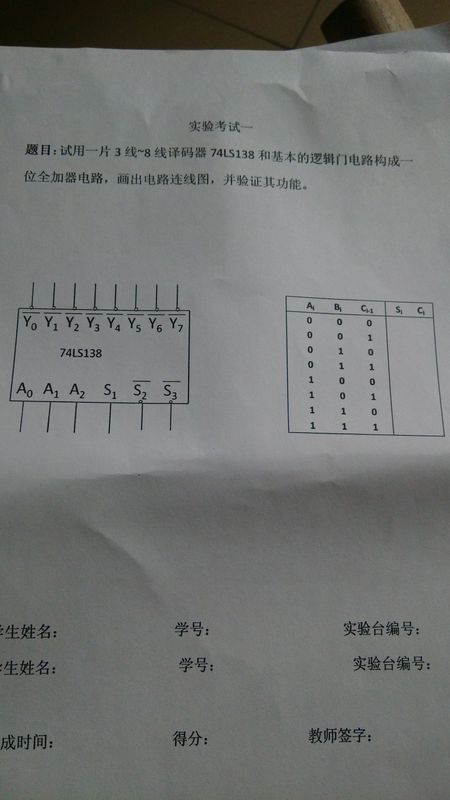

全加器真值表:

00000;00110;01010;01101;10010;10101;11001;11111;

故有Si和Ci的表达式分别为:

Si=A’B’C+A’BC’+AB’C’+ABC

Ci=A’BC+AB’C+ABC’+ABC

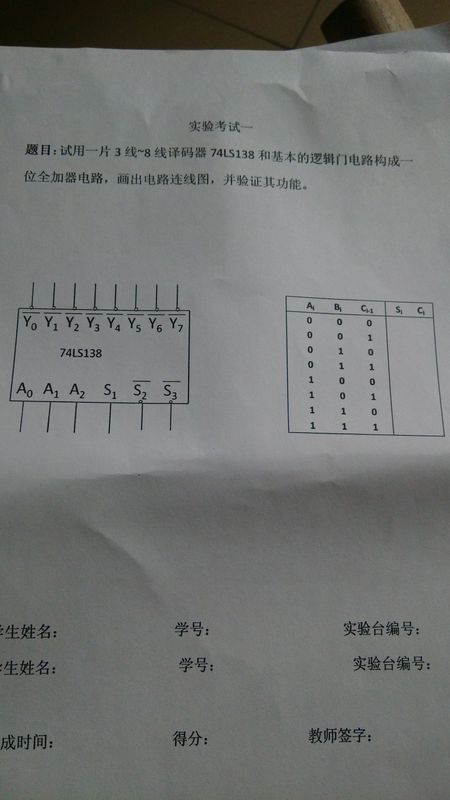

故74138的连接图为:

下面的地址输入端:A2、A1、A0分别接全加器的三个输入信号:Ai、Bi、Ci-1;

下面的使能信号端:S1接高电平"1",S2、S3接低电平"0";

上面的信号输出端:

Y1、Y2、Y4、Y7接至一个四输入与非门的四个输入端,此与非门的输出端为全加器输出信号Si端;

Y3、Y5、Y6、Y7接至一个四输入与非门的四个输入端,此与非门的输出端为全加器输出信号Ci端.

再问: 请问下哈,那个图怎么画,上课没有怎么听的

再答: 我上面的回答不是写得很清楚吗?照着我写的连上每一个端子就0k了。

再问: 好的,我知道了,非常感谢你的回答。

00000;00110;01010;01101;10010;10101;11001;11111;

故有Si和Ci的表达式分别为:

Si=A’B’C+A’BC’+AB’C’+ABC

Ci=A’BC+AB’C+ABC’+ABC

故74138的连接图为:

下面的地址输入端:A2、A1、A0分别接全加器的三个输入信号:Ai、Bi、Ci-1;

下面的使能信号端:S1接高电平"1",S2、S3接低电平"0";

上面的信号输出端:

Y1、Y2、Y4、Y7接至一个四输入与非门的四个输入端,此与非门的输出端为全加器输出信号Si端;

Y3、Y5、Y6、Y7接至一个四输入与非门的四个输入端,此与非门的输出端为全加器输出信号Ci端.

再问: 请问下哈,那个图怎么画,上课没有怎么听的

再答: 我上面的回答不是写得很清楚吗?照着我写的连上每一个端子就0k了。

再问: 好的,我知道了,非常感谢你的回答。

用一篇3线~8先译码器74LS138和基本逻辑电路构成一位全加器电路,画出电路连线图

用3/8译码器74LS138和门电路构成全加器,写出逻辑表达式,画出电路图,

怎样用74LS138译码器构成一位全减器电路

用74LS138译码器构成6-64线译码电路,至少需要多少块74LS138译码器?答案是9块.我知道了,但是为什么?

可否采用一片2线-4线译码器74LS139或一片3线-8线译码器74LS138设计一个全加器.为什么?

数字逻辑分析题求解1、分析下图由3线-8线译码器74LS138构成的电路.(1)写出输出Si和Ci的逻辑函数表达式;(2

用3线-8线译码器74HC138和门电路设计一个全加器

用数字电路的基础器件(比如74LS161计数器和76LS138译码器)可以设计什么实验电路?

用3线—8线译码器(74LS138芯片).四输入与非门实现"三个开关控制一个灯的电路",要求改变任一开关的状态都能控制改

用3-8译码器和与非门设计电路

试用3线——8线译码器74LS138和门电路实现下面多输出逻辑函数

试用3线-8线译码器74LS138和门电路实现下面多输出逻辑函数.这道题是要画